(革新)様式1-4-3(2022-1)

# 令和6年度研究開発成果概要図(目標・成果と今後の成果展開)

採択番号:07901

#### 1. 研究課題・受託者・研究開発期間・研究開発予算

- ◆研究開発課題名 高速大容量データ転送を実現する革新的ハードウェア技術の研究開発

- ◆受託者 国立大学法人東京科学大学、富士通オプティカルコンポーネンツ株式会社、古河電気工業株式会社、古河ネットワークソリューション株式会社

- ◆研究開発期間 令和6年度(1年間)

- ◆研究開発予算(契約額) 令和6年度の総額100百万円

#### 2. 研究開発の目標

日本の強みであるマルチコアファイバ技術を導入し、高速大容量・省電カデータ転送を可能にする革新的ハードウェア技術を開発する。具体的には、

【1】VCSEL/PDアレイと単一モードMCFを用いたSDM(空間多重)方式を適用した超小型CPO(Co-packaged Optics)トランシーバを開発する(伝送速度400/800Gbps、サイズ1cm3以下、消費電力5W以下)。さらに、【2】50Gbaudx16ch超高密度CPOトランシーバに対応した高密度光電インターフェイスを実証し、【3】小型・大容量電

気スイッチ装置の動作実証を行う。

3. 研究開発の成果

研究開発目標

研究開発成果

### 【項目1】:CPO 超小型光トランシーバの研究開発

・面発光レーザアレイ 変調速度>50Gbaud、PAM4 100Gbps 55℃安定動作、消費電力 <0.2pJ/bit

・CPO 光トランシーバ 400Gbps (25Gbps/ch)動作実証

世界最小 ≦1cm<sup>3</sup>(7.8×16×8mm) 消費電力 5W以下

・次世代CPO光トランシーバ

800Gbps (50Gbps/ch)検証

#### ┃研究開発項目1-a: CPO光トランシーバのためのVCSELアレイの研究開発

- ・変調速度 90Gbaud、PAM4 160Gbps、高温55℃で 50Gbaud, 100Gbps

- 消費電力 0.15pJ/bit、MCFとのレンズレス光結合で結合損失<3.5dB</li>

#### 研究開発項目1-b: CPO超小型光トランシーバモジュールの研究開発

- -400Gbps(25Gbps x 16コア)CPO光トランシーバの目標性能を達成: サイズ <1cm³、消費電力 2W (5pJ/bit)、2km SM-MCF伝送

- ・800Gbps (50Gbps x 16コア)次世代CPO光トランシーバの実現性を実証

# 【項目2】: 高密度光電インターフェイス技術の研究開発

2-a)CPO対応電気プラガブルインタフェース 世界最小ピッチの高密度インターフェイス

2-b)スイッチASIC 搭載CPOドータボード チップ間を光で接続

## 研究開発項目2-a:高密度光電インターフェイス技術の研究開発

- -50Gbaud x 16ch CPO光トランシーバ用高密度電気プラガブルインターフェイスの実証

- 高密度電気プラガブルインターフェイスを実装した評価ステーションの構築

- ・評価ステーションを用いた50Gbaud x 16ch CPOトランシーバの特性評価

#### 研究開発項目2-b:チップ間光接続を実現するCPOドータボードの開発

- •CPOドータボードを試作、CPO光トランシーバを装着し動作実証

- ・ひとつのCPO光トランシーバについて、25Gbps x 16レーン を接続

- •100mm角のドータボードに32個配置

#### 【項目3】: 小型大容量スイッチ装置の研究開発

CPO搭載スイッチASIC

複数(4台)のスイッチASICを 一つのボードに収容

スイッチ装置の小型化・ 大容量化を可能に

# 研究開発項目3: CPO光トランシーバを接続可能な小型大容量スイッチ装置の研究開発

- ・従来の"Pizza Box"型スイッチ装置(スイッチ装置にASIC1 個が限界)を脱却したスイッチ装置の大容量化・小型化を実証

- ・100mm角のドータボード4枚をマザーボードに実装

- I・2Uの高さのスイッチ装置で、スイッチ装置4台分のスイッチング能力を実証

#### 4. 特許出願、論文発表等、及びトピックス

| 国内出願     | 外国出願  | 研究論文     | その他研究発表    | 標準化提案・採択 | プレスリリース<br>報道 | 展示会      | 受賞·表彰    |

|----------|-------|----------|------------|----------|---------------|----------|----------|

| 7<br>(7) | 3 (3) | 1<br>(1) | 27<br>(27) | 0<br>(0) | 1<br>(1)      | 2<br>(2) | 2<br>(2) |

#### 面発光レーザアレイ:

※成果数は累計件数、()内は当該年度の件数です。

- ・最終目標を超える90Gbaud、160Gbps(PAN4)の高速動作、0.15pJ/bitの低電力動作を実現。基調講演・招待講演:10件(当該年度)

- ・研究業績に対して、電子情報通信学会功績賞受賞、米国工学アカデミー外国人会員に選出 CPO光トランシーバ:

- ・CPO超小型光トランシーバの成果を世界最高峰の国際学会ECOC 2024に投稿、Upgraded Talkでの講演というトップクラスの高評価を得た。

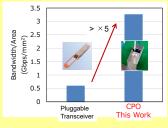

- ・400Gbps (25Gbps × 16チャンネル)、体積1 cm<sup>3</sup> 未満で世界最小の超小型CPO光トランシーバを開発、4.95pJ/bitの低消費電力動作を実証した。 CPO光トランシーバは従来のプラガブル光トランシーバと比較して大きなメリットが期待(消費電力 1/4、伝送容量密度 5倍) 電気インターフェース:

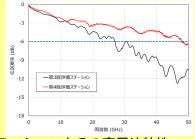

- ・50Gbaud信号に対応した光電インターフェースの実証を目標としてきたが、50Gbaud x 16コアCPO光トランシーバ用に開発した評価ステーションの周波数帯域は、50Gbaudのナイキスト周波数25GHzよりも顕著に大きい47.9GHzが得られ、100Gbaudへ適用できる可能性がある。

- ・国内研究会と国際会議において賞を受賞. エレクトロニクス実装学会関西実装フェスタとIEEE CPMT Symposium Japanより受賞した。 スイッチ装置

- ・FPGA搭載CPOドータボード、小型大容量スイッチ装置を国際シンポジウム(IEEE CPMT Symposium Japan 2022,2023,2024)に展示。 ドータボードで必要となる高密度配線を可能にする技術など特許5件を出願。

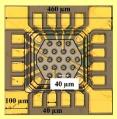

CPO実装可能な高密度面発光レーザアレイと160Gbps(PAM4)変調

400Gbps 超小型CPO光トランシーバ 外観

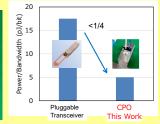

CPO光トランシーバ の効果

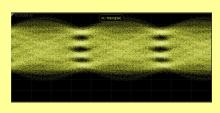

開発した評価ステーションとその高周波特性

FPGA搭載CPOドータボード

小型大容量スイッチ装置

#### 5. 研究開発成果の展開・普及等に向けた計画・展望

研究開発項目1:研究開発項目1マルチコアファイバを用いたCo-Packaged Optics(CPO)超小型光トランシーバの研究開発

#### 【計画】

- ・連携研究者である富士フィルムビジネスイノベーション社と連携して、高速動作可能な1060nm帯結合共振器面発光レーザアレイのチップビジネスに展開。

- ・CPO超小型光トランシーバの実用化に向け、大容量スイッチ装置メーカ等と連携した商品化を目指す。

- ・CPO光トランシーバは新規市場であるため、製品仕様の明確化が重要である。CPO標準化を議論している団体(OIF等)の情報を収集し、また顧客動向・顧客要求の調査を行い、社会実装へ向けた方針検討を行う。

#### 【展望】

- ・結合共振器等の新規構造導入により、面発光レーザアレイの200 Gbps以上の高速化、さらに400 Gbps級の変調速度限界を探索し、優位性を確立。

- ・CPO光トランシーバ標準化を議論している団体(OIF)では、2023年に最初の標準化(IA)を完了しており、市場は立ち上がりつつある。

- ・CPO光トランシーバの市場規模は、2028年には100億円以上の規模に成長する見込みであり、本市場をターゲットとする。

#### 研究開発項目2:チップ間光接続を可能とする高密度光電インターフェイス技術の研究開発

#### 【計画】

- ・CPOに適用される超小型光トランシーバのニーズは、狭い領域で高密度にポートが存在するシステムと高い親和性がある。人工知能/機械学習システムを開発している会社と実用化について議論を進める

- ・光トランシーバの電気と光インターフェイス部分の相互接続性を実現するべく、市場関係者と情報交換及び議論を行う。そのために、本研究の成果を学会等において技術アピールを行っていく。

#### 【展望】

- ・今後5年以内に、CPOが導入され、年間数百万台の光トランシーバが出荷されることが予想される。各社がマルチチップの採用をした新たな構造を模索しており、今後、互換性を担保するために、電気及び光インターフェイスを標準化することが求められると思われるので、本方式の提案を進めていく。

- ・今後、チャンネル当たり200Gbps、400Gbpsの導入が予想されている一方で、消費電力増加を抑制するために、さらなるエネルギー効率の向上が求められる。本研究で実証した評価ステーションの周波数帯域は47.9GHzに達しており、100Gbaud PAM4 (200Gbps)に適用できる可能性がある。

#### 研究開発項目2-b:チップ間光接続を実現するCPOドータボードの開発

研究開発項目3: CPO光トランシーバを接続可能な小型大容量スイッチ装置の研究開発

#### 【計画】

- ・本研究開発のプロジェクトメンバと共に、実用化に向けた動作検証を継続的に進めることを検討し、製品化に向けての課題をクリアしていく方策を立てていく。

- ・実用化に向けた課題としては、大容量、低遅延、低消費電力、妥当コストの両立の点が挙げられ、より一層の研究開発努力を進めていく必要があると考える。

- ・シンポジウムや展示会での発表を通じて、開発した技術をアピールし、プロジェクトメンバと共に、チップベンダ、ファイバメーカ、装置メーカ等とコンソーシアムを結成し、当該光トランシーバおよびそれらを搭載可能な新たな大容量スイッチ装置の製品化の実現を目指す。

#### 【展望】

- ・5年後の2030年代においては、µデータセンタ、データセンタ内極低遅延光スイッチング技術の発展が期待される。その中で、極低遅延スイッチング動作を高密度の光トランシーバ実装による大容量データスイッチングを実現するために、本研究のCPO光トランシーバ、電気プラガブルインターフェイス、スイッチASIC搭載CPOドータボードの実証検証、研究開発を継続した後に、こられの製品化が進み、実用化の段階になると考える。

- ・スイッチ装置は、従来の筐体サイズを保ったまま、CPOドータボードを複数搭載することで容易に大容量化を実現できるという顕著な拡張性を有する。また、フロントパネルにはマルチコアファイバを用いた超高密度光コネクタが配置される等の特徴がある。これらの優位な特徴を同業の装置ベンダと協力して技術を共有し、データセンタ運営会社に技術提案を行う。