### 令和6年度研究開発成果概要図 (目標・成果と今後の研究計画)

## 採択番号: 23701

## 1. 研究課題・受託者・研究開発期間・研究開発予算

◆研究開発課題名:完全自動運転のための高性能かつ高信頼な車載光ネットワーク基盤技術の研究開発

◆副題 :コヒーレント光フレームスイッチ方式を用いた車載通信システムの拡張性向上と省電力化に関する研究開発

◆受託者 :学校法人慶應義塾、古河雷気工業株式会社、公立大学法人滋賀県立大学、国立大学法人東海国立大学機構「岐阜大学、

国立大学法人大阪大学、株式会社ファストリンクテック

◆研究開発期間 : 令和6年度~令和8年度(3年間)

◆研究開発予算(契約額) : 令和6年度から令和7年度までの総額220百万円(令和6年度120百万円)

## 2. 研究開発の目標

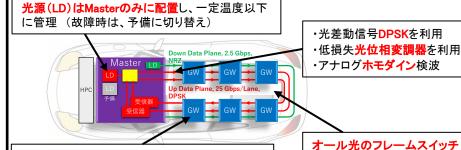

石英シングルモード光ファイバによってゾーン分割型構成に基づく車載光ネットワークを構築し、コヒーレント光フレームスイッチ方式を利用 して、マスター装置と各ゾーンに配置されるゲートウェイ装置間でレーンあたり25Gbpsの伝送速度で100Gbps以上の大容量通信を可能とする。

## 3. 研究開発の成果

方式を採用。GWを光のまま

通過し、OEO変換は一切行

わない

## 研究開発項目1:車載光通信装置の開発

DPSK光信号を生成する送信用ドライバ回路を消費電力1W以下で実現し、広帯域LN位 相変調器を試作する。DPSK光信号を受信し電気信号に変換する受信回路を消費電力1 W以下で実現する。マスター装置からGW装置間で下り2.5GbpsのIMDD伝送、上り 25Gbps/chのホモダイン検波によるDPSK変調方式に基づく車載光伝送を実現する。

## 研究開発項目2: 車載光ネットワークシステム及び通信方式の開発

6台以上のGW装置を接続し、ネットワーク遅延時間を2μs以下とする車載光ネットワー クを構成する方法を明らかにする。EMC評価および温度変化等の外部環境に対する耐 力試験を実施し、実用化に向けた指針を得る。

## 本研究の車載光ネットワーク構成

- 電気スイッチの削除

- ・ドライバ、TIA等の削減

- •GWのドライバは指定時のみ動作(Sleep mode)

# 研究開発目標

## 光送信回路

25Gbps動作でプッシュプルで位相変調器を駆動する EICの設計を実施。

動作速度: 25 Gbps 消費電力: 500 mW/ch 以下

#### マスター/GW装置

位相変調器および駆動用Tx-EICを実装する光モ ジュールを設計、パッケージを試作。また、Tx/Rx-EICを 評価するためのインターポーザ基板を設計、試作。 FPGAとの25Gb/s差動電気伝送回路の設計検証を実施。 高速シリアルインタフェース搭載の小型FPGAボードで 25Gbps、BER<10<sup>-12</sup>のエラーフリー伝送性能を確認。

位相変調器光モジュールパッケージ

EICインターポーザ基板

FPGA接続差動伝回路特性

小型FPGAボード(SOM)

研究開発成果

## 光受信回路

25Gbps動作に必要な1ビット遅延量および温度変化 に伴う遅延量誤差の相殺に必要な可変幅が得られる 回路構成を決定。

#### 遅延回路チップレイアウト 遅延量可変幅と温度依存性

## 車載NW構成検討

映像系トラヒックの低遅延化・低ジッター化が 可能であることを確認。

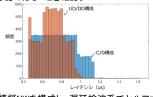

模擬NWを構成し、遅延検波系でセルフホモ ダイン伝送特性を検討。

## 4. 特許出願、論文発表等、及びトピックス

| 国内出願     | 外国出願  | 研究論文     | その他研究発表  | 標準化提案・採択 | プレスリリース<br>報道 | 展示会      | 受賞·表彰    |

|----------|-------|----------|----------|----------|---------------|----------|----------|

| 3<br>(3) | 0 (0) | 0<br>(0) | 5<br>(5) | 0 (0)    | 0<br>(0)      | 0<br>(0) | 0<br>(0) |

※成果数は累計件数、()内は当該年度の件数です。

## 5. 今後の研究開発計画

コヒーレント光フレームスイッチ方式を用いた車載通信システムに対応する高速光位相変調用EICの実現に向け、NRZ-DPSK変換および光位相変調器ドライバを混載した回路の集積化に向けた詳細設計を行う。チップサイズは2 mm × 2 mm、2チャンネル搭載、動作速度は25 Gbps、消費電力は1 W以下を目標とする。また、フレームスイッチ方式に対応した消費電力削減技術の開発を進めるとともに、プロセスや温度変化に対する補正技術を確立する。さらに、LN光位相変調器の高速電気伝送線路の設計を行い、システム全体の性能向上を図る。

DPSK復調回路における遅延回路の遅延量制御特性の最適設計手法の検討結果をもとに、DPSK復調回路チップの設計・試作を行い、基本動作を実証する。 65-nm CMOSプロセスを適用し、1チャンネルあたりのビットレート 25 Gbps程度、チップサイズ 2 mm × 2 mm 程度、消費電力 1 W 程度を目標とする。光素子や光受信回路と、DPSK復調回路試作チップを組み合わせたDPSK光位相変調信号の復調動作の評価に向けた検討を行う。

薄膜LN位相変調器デバイスの試作および評価を実施する。UD-plane位相変調器光モジュールをモジュールへ実装し、評価を実施する。UD-Planeコヒーレント受信器モジュール試作および評価を行う。まず、Rx-EICをインターポーザ基板へ実装し、評価する。また、FPGA接続用ICRボードを試作し、ICRおよびRx-EICインターポーザ基板を実装し、FPGAと組み合わせて動作確認を行う。DD-plane送受信光モジュール、光受信モジュールを筐体へ実装する。マスター装置、GW装置の筐体設計を完了し、電源を試作する。

SOM評価ボード同士を対向接続し、UD-Plane/DD-Planeを電気的に模擬することで、簡易的なマスター/GWとして動作させ、定義した信号フレームフォーマットの基本機能が実機において問題なく機能することを検証する。また、製造したI/OボードとSOMを組み合わせ、基本的な動作を確認する。さらに、マスター/GW装置で使用するPMボードとICRボードを接続し、UD-Planeにおける光信号の変調/復調動作を検証する。

本研究開発における車載光ネットワークが高信頼であることを示す。そのために、平均故障時間MTTF(Mean Time To Failure)の算出と、摩耗故障期の故障・ 多重故障に対応するNW通信方式の開発に取り組む。

ホモダイン検波によるコヒーレント変復調方式における伝送特性をシミュレーションによって明らかにし、実環境を想定した伝送性能を明らかにする。DPSK遅延 干渉計を利用した送受信系を構築し、シミュレーションと対比しながら車載用コヒーレント伝送系の最適化を検討し、コヒーレント受信器を利用したホモダイン検波 による受信波形の再構築をオフラインで行い、コヒーレント変復調システムの最適化設計指針を得る。本研究開発の車載光ネットワークの冗長性や省電力性を生 かした制御系データ通信技術の検討において、車載光ネットワークの一部レーンのネットワーク障害等が発生した場合でも制御性能の劣化を抑制しつつトラヒック 量削減が可能である見込みを得る。